# University of California, Santa Barbara

Department of Electrical and Computer Engineering

ECE 152A – Digital Design Principles

Midterm Exam #1 – Solution October 19, 2006

| Name                   |  |  |  |  |

|------------------------|--|--|--|--|

| Perm #                 |  |  |  |  |

| Lab Section            |  |  |  |  |

|                        |  |  |  |  |

| Problem #1 (20 points) |  |  |  |  |

| Problem #2 (20 points) |  |  |  |  |

| Problem #3 (20 points) |  |  |  |  |

| Problem #4 (20 points) |  |  |  |  |

| Problem #5 (20 points) |  |  |  |  |

| Total (100 points)     |  |  |  |  |

- This is a 75 minute exam; closed book, closed notes, no calculators.

- Answer all questions on the paper provided by the instructor.

- Write on only one side of the paper.

- Attach answer sheets to this exam in the correct order.

- Include your name and perm # on every sheet.

#### Problem #1.

1. Using only Boolean algebra, convert the following Sum of Products expression to <u>simplified</u> Product of Sums representation.

AB+BCD+BCD+ACD CONVERT TO POS ... PIMPLIFY FIRST A'B + B'D(C'+C) + A'C'D A'B+B'D +A'C'D CONSENSUS TERM = A'D ... + A'C'D = A'B+B'D Pos: (A'+B'D)(B+B'D) 10 (A'+B')(A'+D)(B+D) (A'+B')(B+D) (A'+B')(B+D)

A'B + B'C'D + B'CD + A'C'D

2. Again, using only Boolean algebra, convert the following Product of Sums expression to <u>simplified</u> Sum of Products representation.

(B' + C)(A + C' + D')(A + B')(A' + C' + D')

(B'+C)(A+C'+D')(A+B')(A'+C'+D') = (C'+D') (B'+C) (C'+D') (A+B') B'+C C'+D' B'C' + C/C + B/D' + CD' CONSERVUS = B'D' B'C'+CD' A+B' AB'C' + ACD' + B'C' + B'CD' - ABSORPTIONI ACD'+B'C'+B'CD' ACD'+B(C'+CD') ACD'+B'(C'+D') = ACD' + B'C' + B'D'

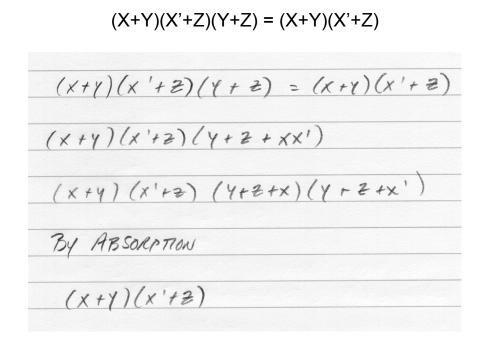

3. Again (and finally), using only Boolean algebra, prove the following theorem:

## Problem #2.

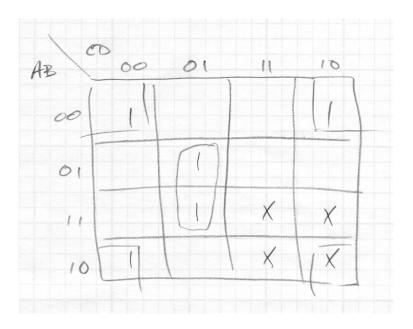

- 1. Map the following sum of minterms function on a Karnaugh map:

- $\Sigma$  m = (0,2,5,8,13) + d(10,11,14,15)

2. Identify all prime and essential prime implicants and minimize the function.

3. Is the minimized sum of products expression unique (and why or why not)?

UNIQUE BECAUSE COVER INCLUDES ONLY ESSENTIAL PRIME FAMPLICANTS

4. As implemented in part 2 above, express the minimized function in sum of minterms form.

Z.M. (0, 2, 5, 8, 10, 13)

5. Express the same function from part 1 above, in product of maxterms form.

TIM (1,3,4,6,7,9,12). d(10, 11, 14, 15)

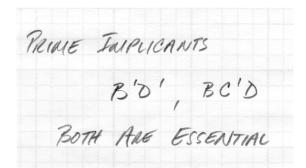

6. Map the product of maxterms function, identify all prime and essential prime implicants and minimize the function.

CD 10 00 01 11 AB ()00 0 01 11 X C 10 X PRIME TAIPLICANTS (B'+D) (B+D'), (C'+D'), (B'+C') A A ESSENTIAL PRIME TUPLICANTS

7. Is the minimized product of sums expression unique (and why or why not)?

NOT UNIQUE = (B'+D)(B+D')(C'+D')or = (B'+D)(B+D')(B'+C')

8. As implemented in part 6 above, express the minimized function in product of maxterms form.

TTal= (1,3,4,6,7,9,11,12,14,15)

Midterm Exam #1 – Page 6 of 17

## Problem #3.

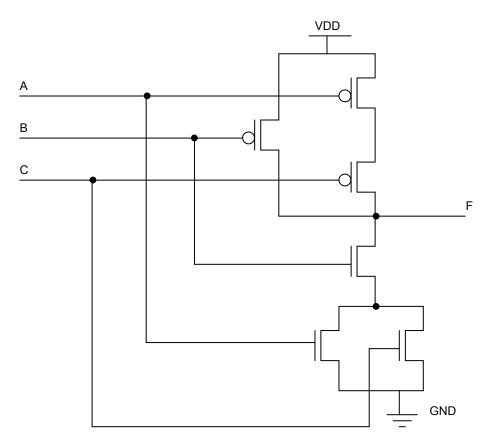

The static CMOS gate shown below is knows as a "complex gate" because it includes both parallel and serial paths in both the pull-up network (pMOS transistors to logic "1") and the pull-down network (nMOS transistors to logic "0").

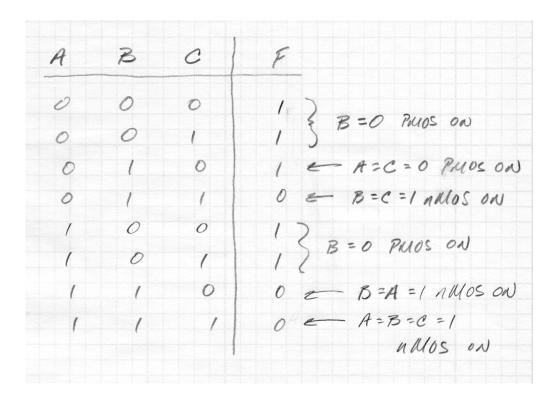

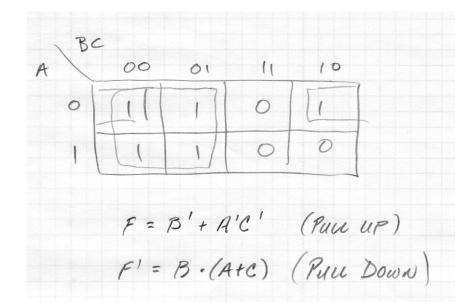

1. Construct the truth table for the compound gate shown below.

2. What function is implemented (Boolean expression) by this gate?

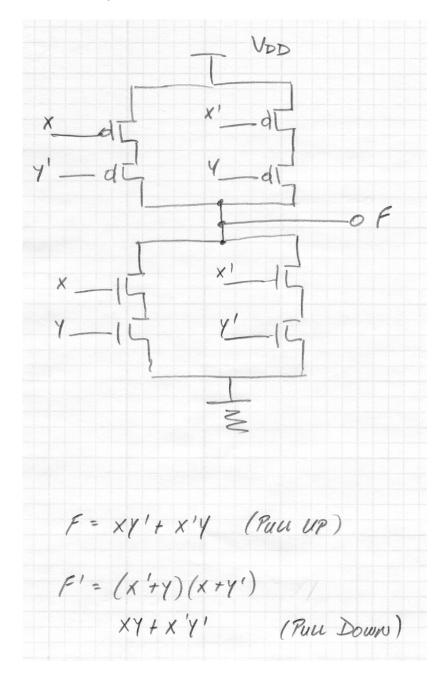

3. The sum output of a half adder (XOR) can be constructed from a single, complex gate, assuming both the true and complemented versions of both inputs, x and y, are available (i.e., x, x', y and y').

Design the complex CMOS gate that implements the sum output of a half adder. As always, use pMOS transistors to pass "1's" to the output and nMOS transistors to pass "0's".

#### Problem #4.

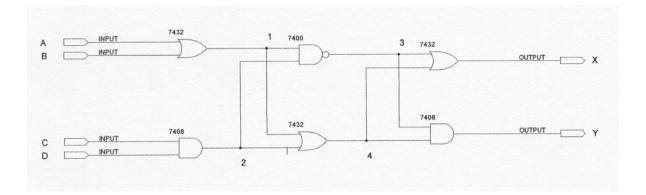

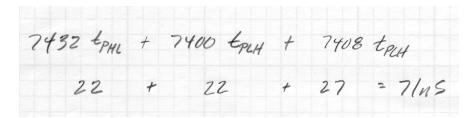

For the network shown below, determine the critical path and maximum propagation delay. The NAND, AND and OR gates have the following propagation delays:

|      |      | t <sub>PLH</sub> | t <sub>PHL</sub> |

|------|------|------------------|------------------|

| 7400 | NAND | 22ns             | 15ns             |

| 7408 | AND  | 27ns             | 19ns             |

| 7432 | OR   | 15ns             | 22ns             |

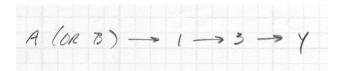

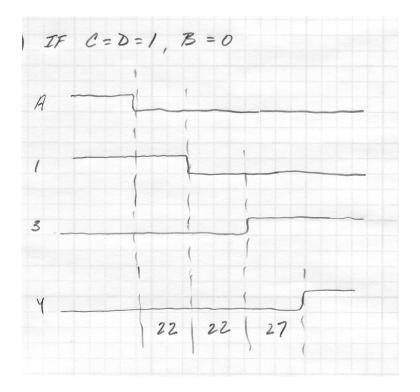

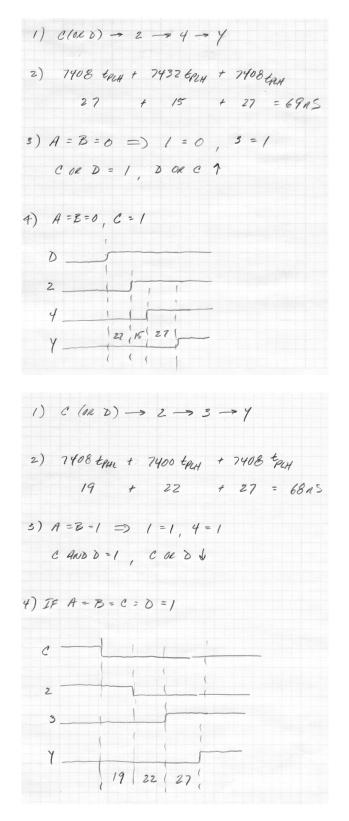

1. Define the path from input to output and identify the nodes (indicated 1, 2, 3 and 4 on the schematic) constituting the critical path. Be sure to take inversions into account when determining the maximum propagation delay.

2. What is the maximum propagation delay and how is it determined (which propagation delays are used in the calculation)?

3. What must the other inputs be in order to allow the signal to propagate from the input to the output?

C=D=1=> Z=1, 4=1 AORB = 1, A OR B J

4. Construct a timing diagram illustrating the delays along the critical path (showing all relevant internal nodes) and including both the X and Y outputs.

Other paths within 5% of 71ns path:

Problem #5.

In this problem you are to design a portion of the circuitry that locks the doors and opens the windows of my car.

There are four inputs to the circuit: the remote unlock button (R) on my key, the door lock button (B) on the console inside the car, an input indicating the status of the door locks (L : 1 when locked, 0 when unlocked) and an input indicating whether the car doors are open or closed (D : 1 when all are closed, 0 when any are open).

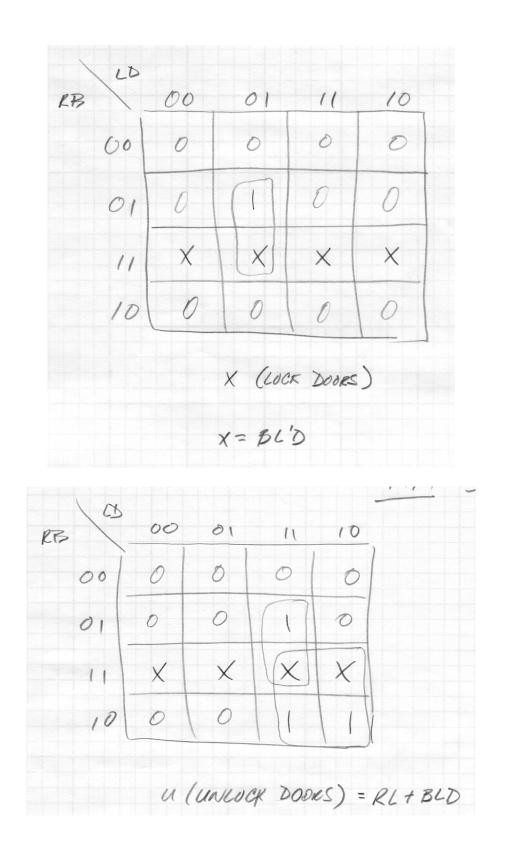

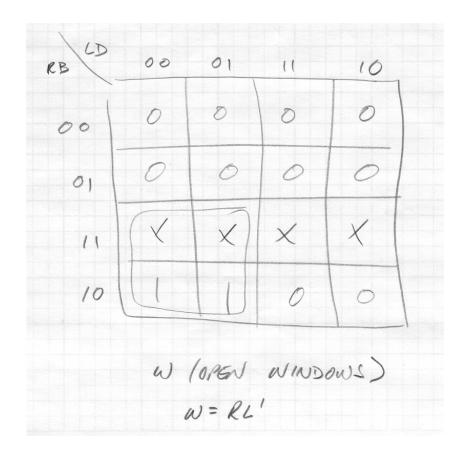

The circuit has three outputs: lock doors (X), unlock doors (U) and open windows (W).

The interior door lock button only works when all of the doors are closed. When pressed with the doors locked, the doors are unlocked. When pressed with the doors unlocked, the doors are locked.

The remote unlock button unlocks the doors when the doors are locked and opens the windows when the doors are unlocked. The remote unlock button does not work inside the car and works whether the doors are open or closed.

Design the 4-input, 3-output circuit that implements this door entry system. Specify your design in sum of products form and clearly identify any assumptions. You don't have to draw the circuit; the simplified Boolean function is adequate.

CONTROL R: RENIOTE UNLOCK B: DOORLOCK BUTTON (INTERIOR) ENSONS Dove Lock Stanus CAR DOOR STATUS

Midterm Exam #1 – Page 14 of 17

There is also a remote lock button ("RL") on my key. When the doors are unlocked and the remote lock button is pressed, the doors are locked. If the doors are already locked, the interior lights ("IL") are illuminated. Like the remote unlock button, it does not work inside the car and it's ergonomically impossible to press the remote lock and remote unlock buttons at the same time.

2. Add the remote lock input and the interior light output to the circuit designed above. Again, as above, specify your design in sum of products form and clearly identify any assumptions. You don't have to draw the circuit; the simplified Boolean function is adequate.

REMOTE LOCK BUTTON · AFFECTS X (LOCK DOORS) AND FL (M.). . PREVIOUSLY X = BLD L DODES CLOSED DODES UNLOCKED . BUTTAN IL (INTERIOR LIGHTS) · Now: W RB 00 01 10 11 0 1) 00 X X X 01 X X X X 11 X 10 X RL=1 X (LOCK DOORS)

· WITH RL=0 X = BE'S (AS REFACE) · WITH RL=1 X= RL·L' => X= BLD + RL·L' BY INSPECTION, IL = RL.L